在科技日新月异的今天���,高精度的时间测量已经成为了各个领域不可或缺的一部分。其中���,高精度子母钟系统以其卓越的性能和稳定的输出���,成为了科研领域的首选。本文将深入探讨高精度子母钟系统的输出理论���,希望能为读者提供一个全面而深入的理解。

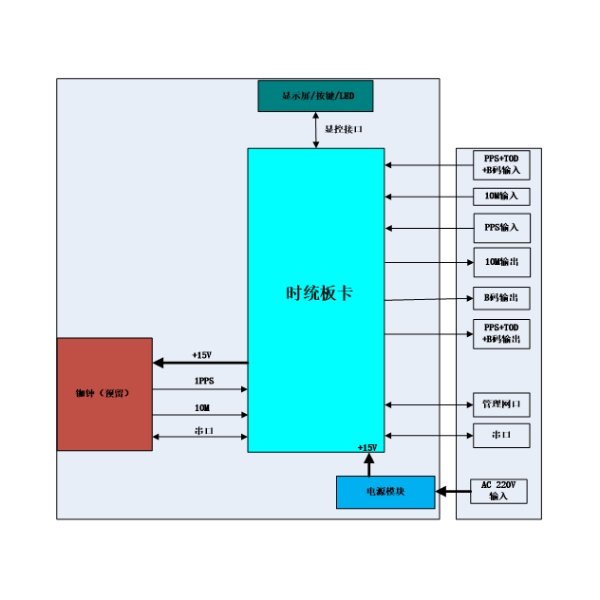

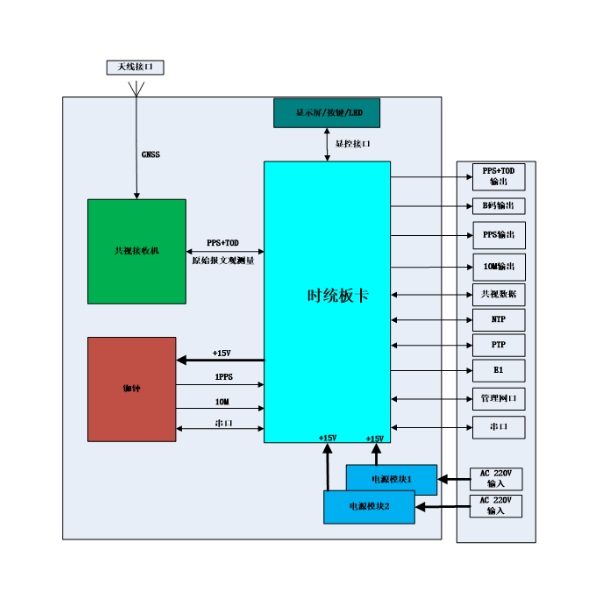

首先���,我们需要明确什么是高精度子母钟系统。子母钟系统由一台主时钟和若干从时钟组成���,它们通过锁相环路进行同步���,从而实现精准的时间计量。主时钟作为系统的“大脑”���,负责产生并控制从时钟的运行。从时钟则按照主时钟的频率进行振荡���,输出稳定���、准确的时间信号。

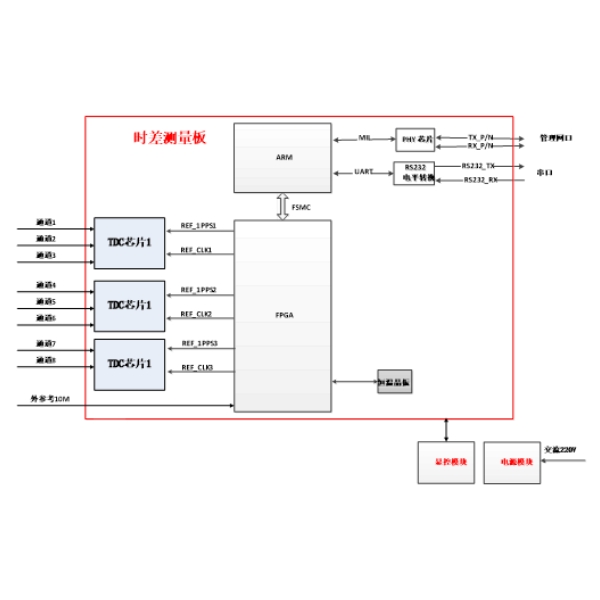

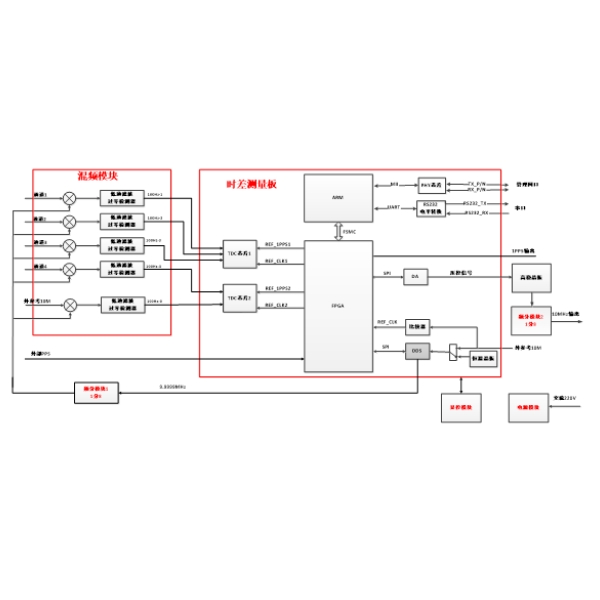

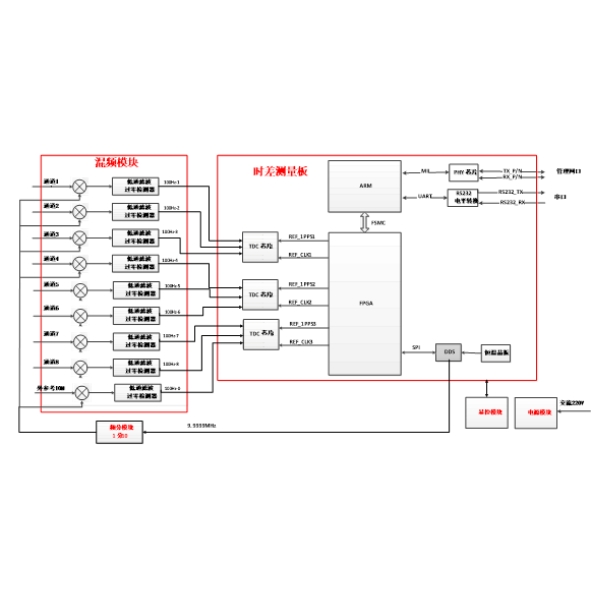

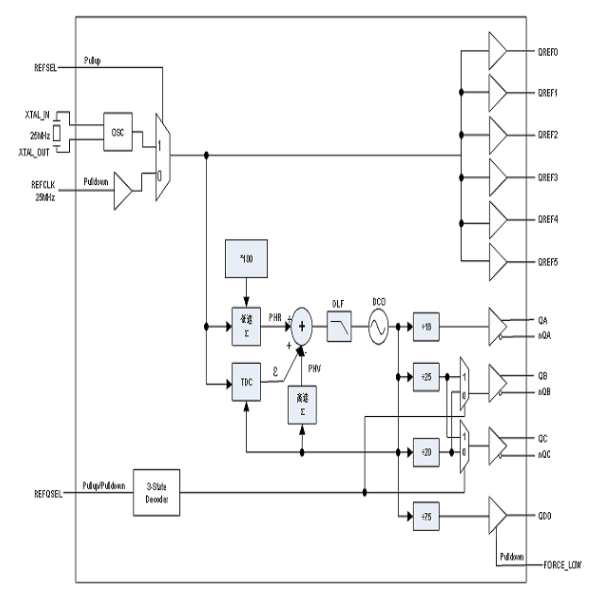

那么���,高精度子母钟系统的输出理论是如何实现的呢?这主要依赖于锁相环路(Phase-locked Loop,简称PLL)技术。PLL是一种反馈控制系统���,通过比较输入信号和期望信号之间的相位差���,来调整电路的参数���,使得系统的输出与期望信号尽可能接近。在子母钟系统中���,PLL被用来调节从时钟的频率和相位���,以保证其输出的时间信号与主时钟同步且误差最小。

除了PLL技术���,高精度子母钟系统的输出还受到其他因素的影响。例如���,温度的变化会影响电子元器件的工作状态���,从而影响系统的时间精度;电磁干扰也可能对系统的稳定性造成影响。因此���,为了提高系统的稳定性和精度���,需要对这些因素进行适当的处理和控制。

总的来说���,高精度子母钟系统的输出理论是一个涉及到电子���、光学���、计算机等多个领域的复杂问题。通过对这个理论的研究和应用���,我们可以更好地理解和控制高精度时间的产生和传播���,为科研���、医疗���、工业���、交通等领域提供精准���、可靠的时间服务。

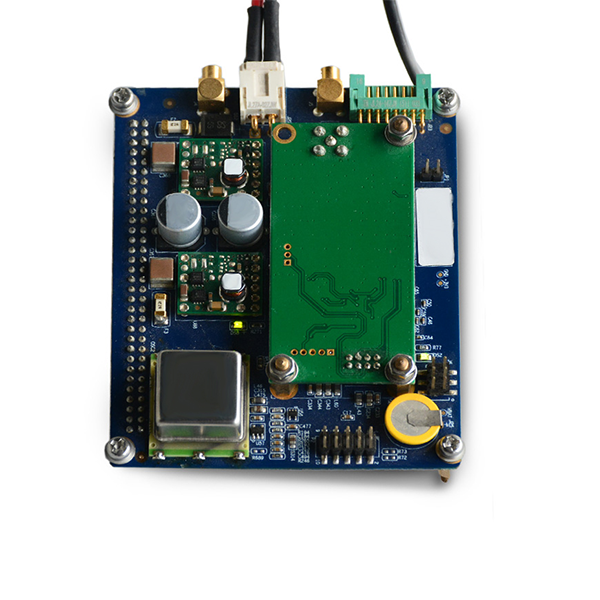

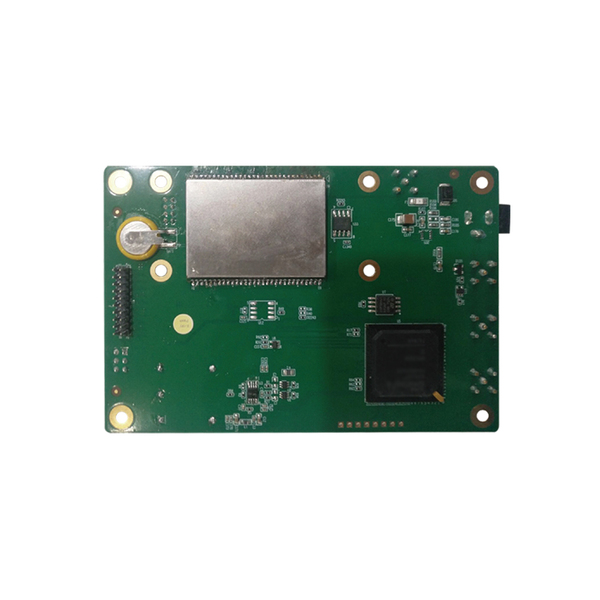

时钟系统

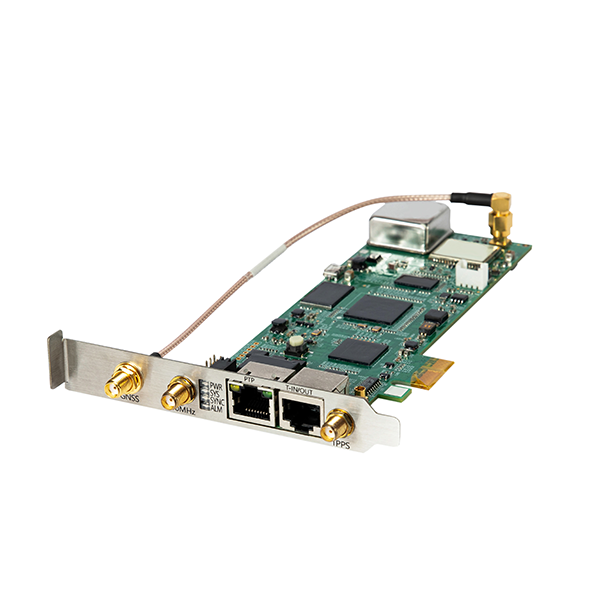

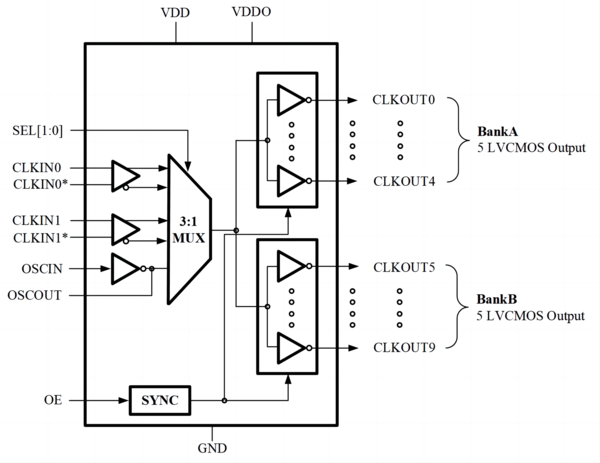

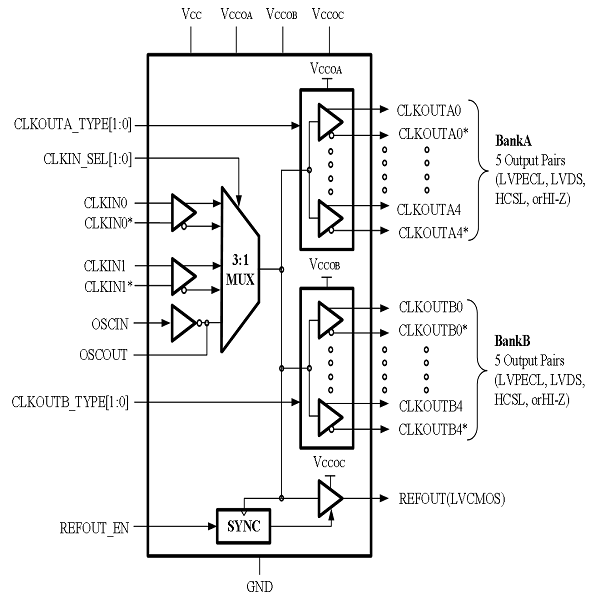

时钟系统  芯片

芯片  晶振&原子钟

晶振&原子钟  授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

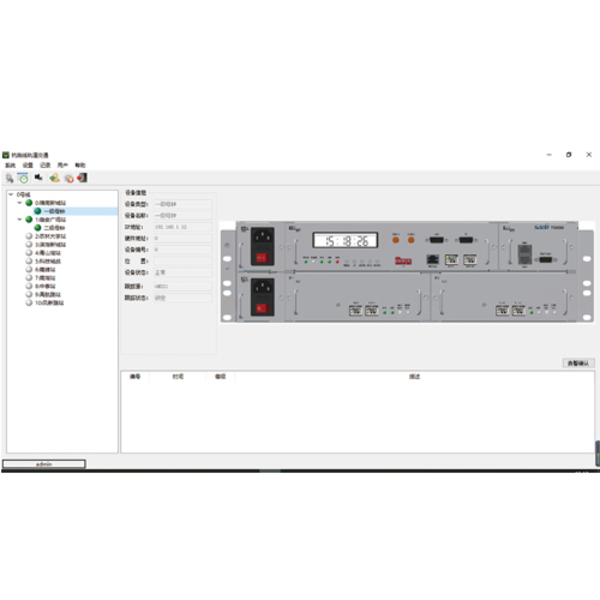

授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

智能电网

智能电网

通信网络

通信网络

智慧交通

智慧交通

智能楼宇

智能楼宇

数据中心

数据中心

前沿领域

前沿领域

新闻资讯

新闻资讯

联系我们

联系我们

人才研学中心

人才研学中心

加入赛思

加入赛思

关于赛思

关于赛思