在高速数字电路设计中���,时钟信号如同系统的心跳���,任何微小的时序偏差都可能引发连锁反应。而时钟缓冲器作为信号完整性的"守门人"���,其选型直接影响着系统稳定性���、功耗表现和成本控制。工程师常面临这样的困境���:参数表上琳琅满目的指标如何转化为设计优势?本文将拆解选型过程中的关键决策因子���,助您在复杂的应用场景中快速锁定最优解。

一���、基础参数决定选型基准

1.1 输入/输出类型匹配度

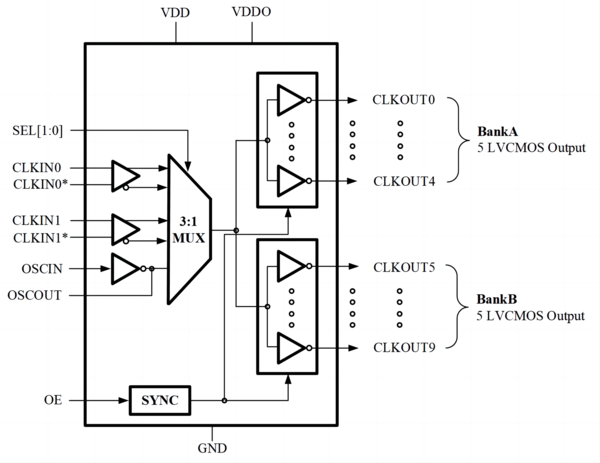

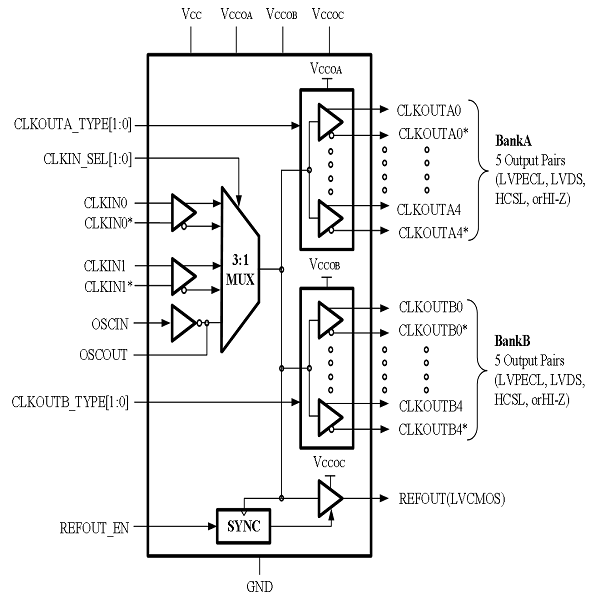

时钟缓冲器的接口必须与主时钟源和负载端完全兼容。LVDS���、LVPECL���、HCSL等差分信号类型需严格对应���,单端信号则需确认电压标准(如1.8V/2.5V/3.3V)。例如���,Xilinx UltraScale+ FPGA的参考时钟若采用HCSL输出���,配套缓冲器应支持HCSL输入转LVDS输出功能。

1.2 抖动性能的量化评估

抖动参数需分层解读���:

周期抖动(Period Jitter)���:直接影响同步电路建立/保持时间余量

相位噪声(Phase Noise)���:在射频系统中决定频谱纯度

附加抖动(Additive Jitter)���:缓冲器自身引入的噪声应小于系统总预算的10%

二���、应用场景驱动的差异化选型

2.1 通信设备���:低抖动优先

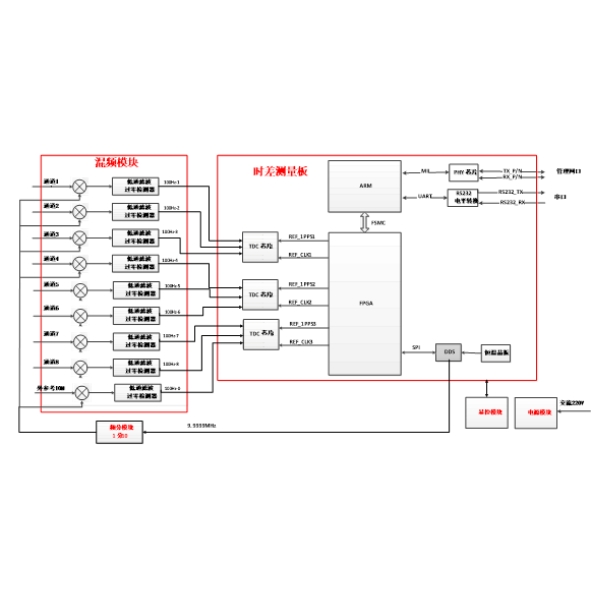

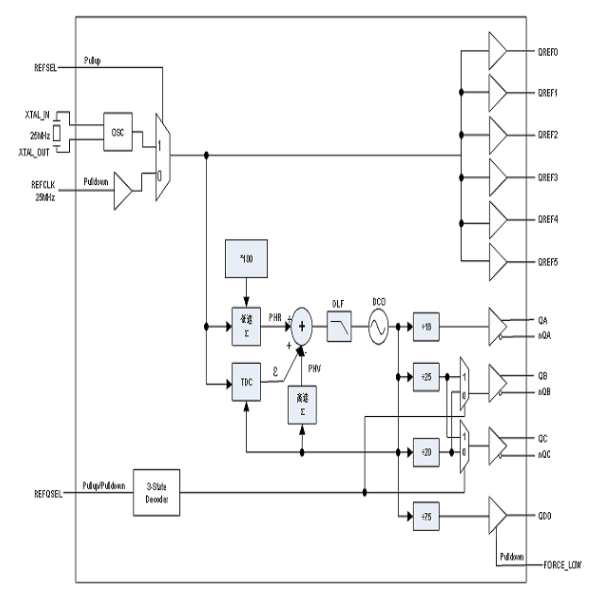

在5G基站或光模块中���,时钟信号需穿越多个时钟域。推荐使用集成PLL的智能缓冲器���,支持输入时钟丢失自动切换功能���,确保系统在±50ppm频偏下仍能维持锁定。

2.2 消费电子���:成本与功耗平衡

智能手表等设备需在静态功耗<1μA与动态响应速度间取舍。采用多电压域设计的缓冲器可动态关闭空闲通道���,实测数据显示其功耗比传统方案降低43%。

通过系统化评估时钟缓冲器技术参数���、应用场景���,工程师可构建完整的选型决策矩阵。在具体实践中���,建议使用参数权重评分法���,对抖动���、功耗���、成本等指标赋予差异化权重���,通过量化分析找到最优平衡点。

时钟系统

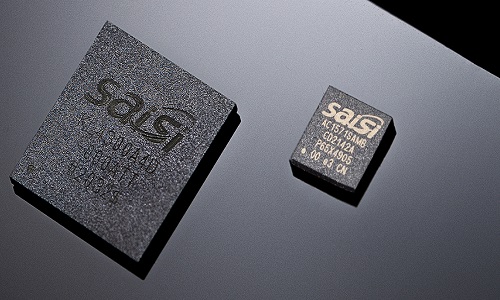

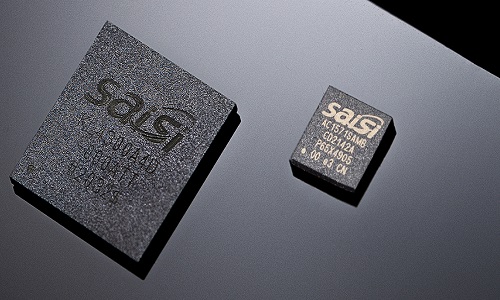

时钟系统  芯片

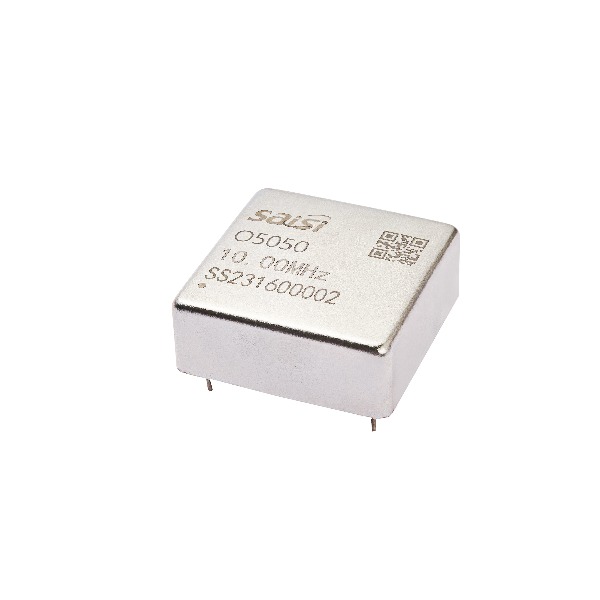

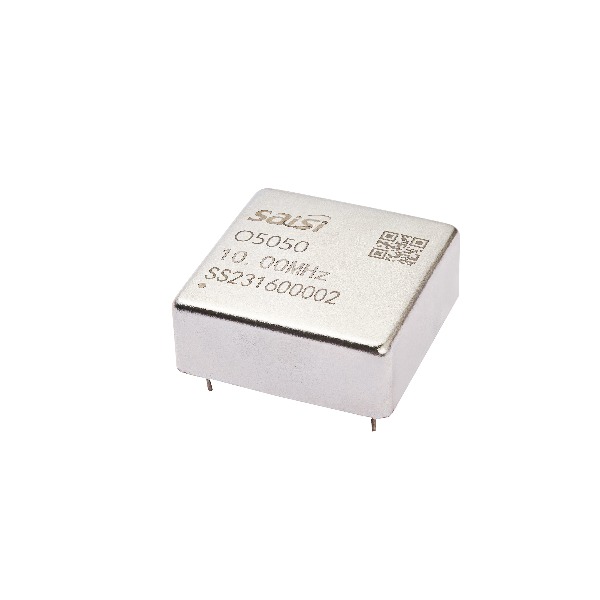

芯片  晶振&原子钟

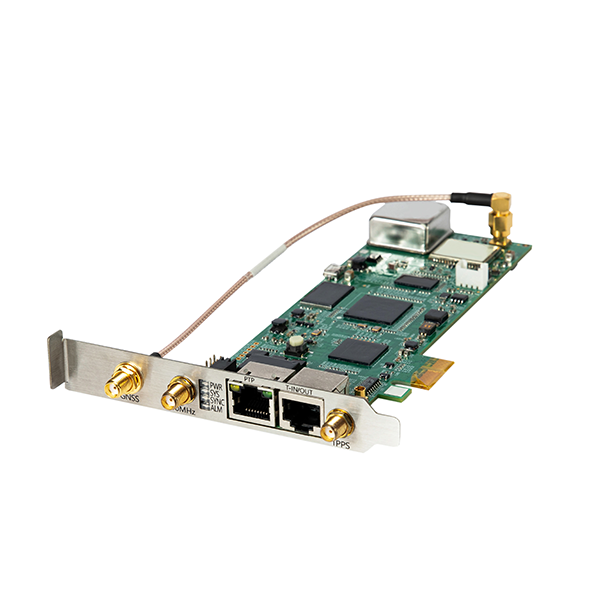

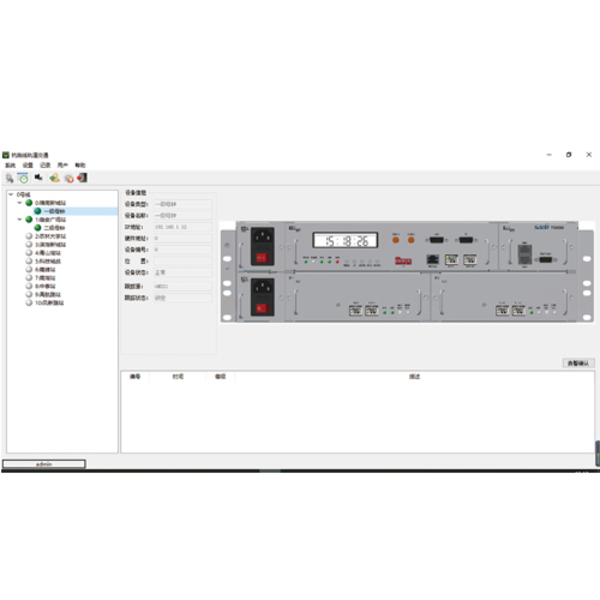

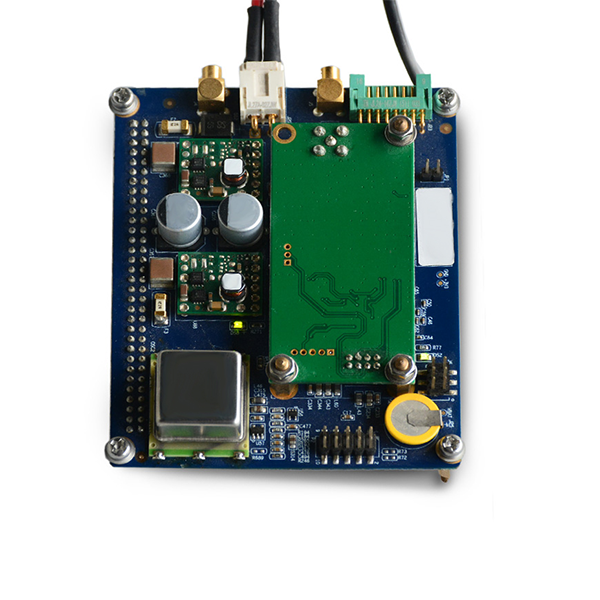

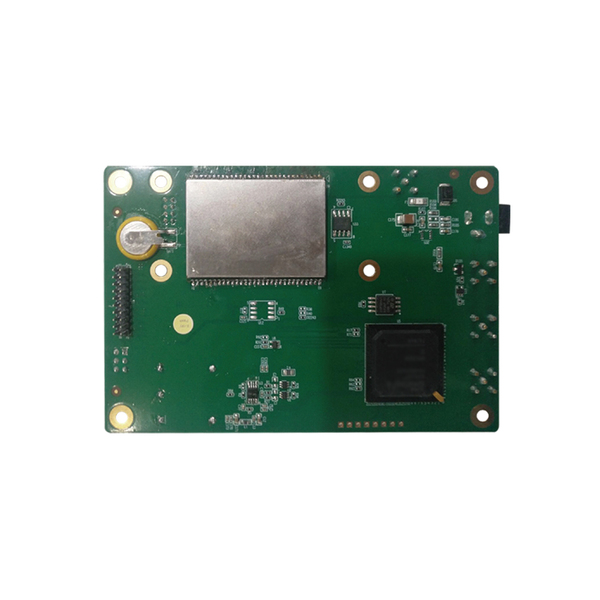

晶振&原子钟  授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

智能电网

智能电网

通信网络

通信网络

智慧交通

智慧交通

智能楼宇

智能楼宇

数据中心

数据中心

前沿领域

前沿领域

新闻资讯

新闻资讯

联系我们

联系我们

人才研学中心

人才研学中心

加入赛思

加入赛思

关于赛思

关于赛思