“时钟信号是电子系统的脉搏���,而时钟缓冲器则是维持其稳定跳动的关键元件。”在高速数字电路设计中���,时钟信号的完整性直接影响着系统性能。随着处理器主频突破GHz级���、多核架构普及以及物联网设备对低功耗需求的激增���,时钟缓冲器已从辅助元件演变为系统级设计的重要支撑。本文将深入剖析时钟缓冲器在五大领域的创新应用���,揭示其如何通过信号整形���、相位同步���、功耗优化等技术手段���,推动现代电子系统突破性能瓶颈。

一���、高速数字系统的时钟树优化

在FPGA���、GPU等超大规模集成电路中���,时钟信号需要驱动数百个终端负载。传统直接驱动方式会导致时钟偏移(Clock Skew)累积���,造成时序错乱。

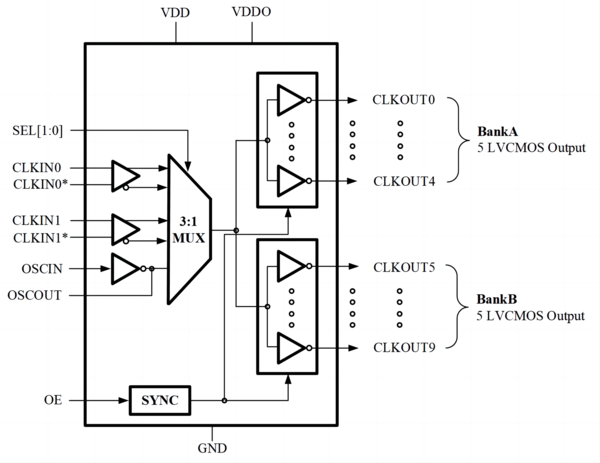

时钟扇出扩展���:通过级联低阻抗输出缓冲器���,将单一时钟源扩展至128路同相信号

阻抗匹配补偿���:内置可编程终端电阻(50Ω/75Ω/100Ω)消除传输线反射

动态延迟调节���:集成数控延迟线(步进精度10ps)修正布线差异

二���、多处理器架构的时钟域管理

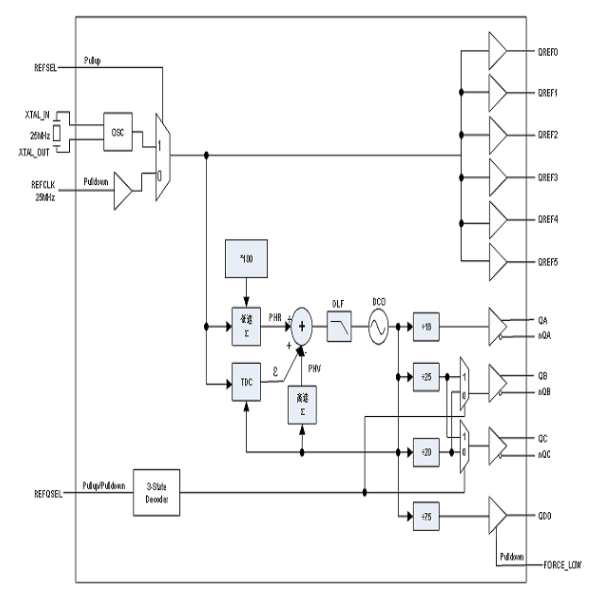

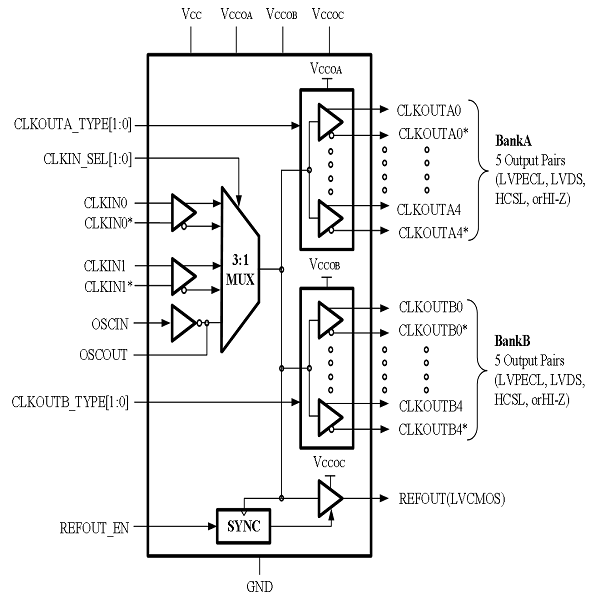

异构计算平台常包含ARM核���、DSP模块和硬件加速器���,各单元工作频率差异可达5倍以上。差分时钟缓冲器通过以下技术实现跨时钟域协同���:

1. 多频点生成���:基于PLL的倍频/分频电路���,从100MHz基准生成1.2GHz/800MHz/200MHz三组时钟

2. 相位对齐���:内置鉴相器自动校准DDR4内存控制器与CPU的时钟边沿

3. 抖动过滤���:采用LC谐振腔滤除开关电源引入的10-100MHz带内噪声

三���、高速通信接口的信号完整性保障

PCIe 5.0���、400G以太网等接口的速率突破32Gbps后���,时钟质量成为链路稳定的生命线。时钟缓冲器在光模块中的应用证明���:

预加重处理���:通过可调预加重电路(0-6dB)补偿FR4板材的高频衰减

共模噪声抑制���:差分架构将CMRR指标提升至45dB@10GHz

四���、可编程逻辑器件的动态重构支持

FPGA的Partial Reconfiguration技术需要时钟网络动态切换。时钟缓冲器通过以下创新满足需求���:

热插拔时钟切换���:采用无缝切换技术(Glitch-Free Switching)���,切换时间<1ns

多区域供电���:支持1.0V/1.2V/1.8V混合电压域驱动

动态功耗调节���:根据负载数量自动调整驱动强度���,静态功耗降低67%

五���、物联网设备的低功耗时钟架构

针对NB-IoT等电池供电设备���,时钟缓冲器突破传统方案局限���:

纳米级功耗管理���:深度休眠模式电流仅850nA���,唤醒时间<2μs

温度补偿算法���:在-40℃~85℃范围内保持±5ppm频率稳定度

从上述应用可见���,时钟缓冲器已超越简单的信号驱动功能���,正在向智能化���、自适应化方向演进。随着3D封装���、光互连等新技术普及���,其设计理念将持续重构电子系统的时钟架构范式。

时钟系统

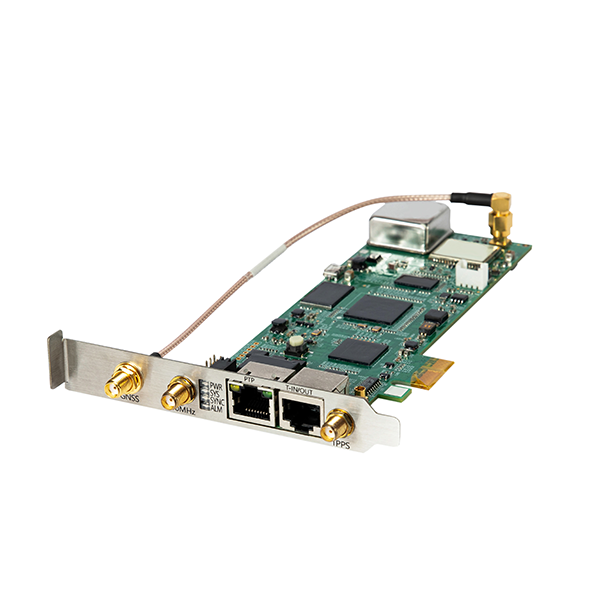

时钟系统  芯片

芯片  晶振&原子钟

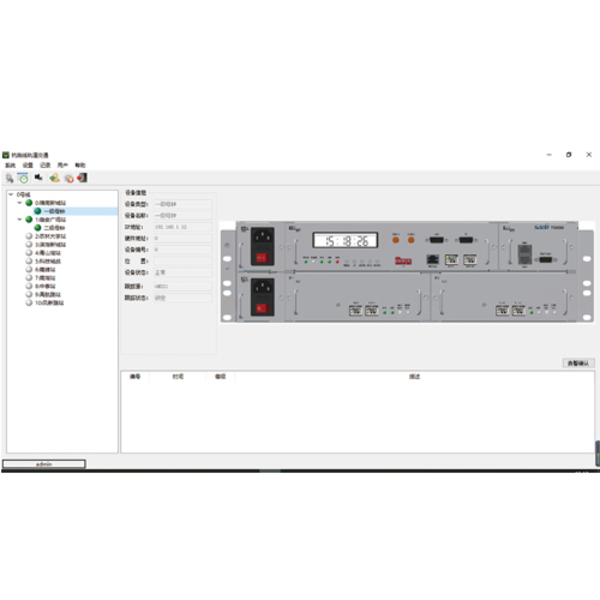

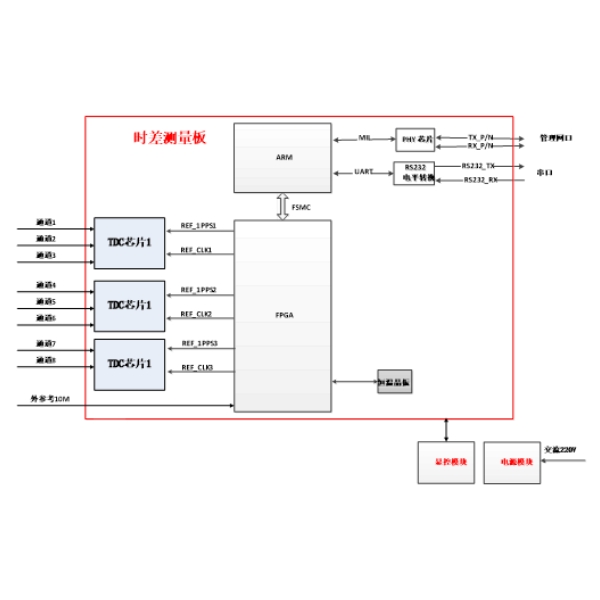

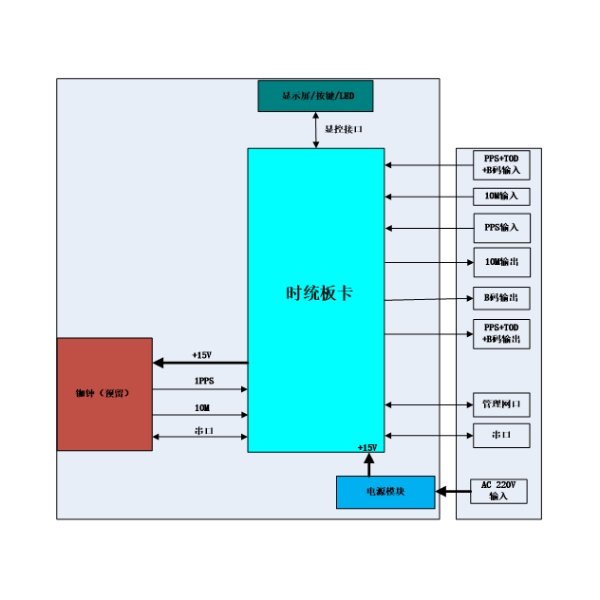

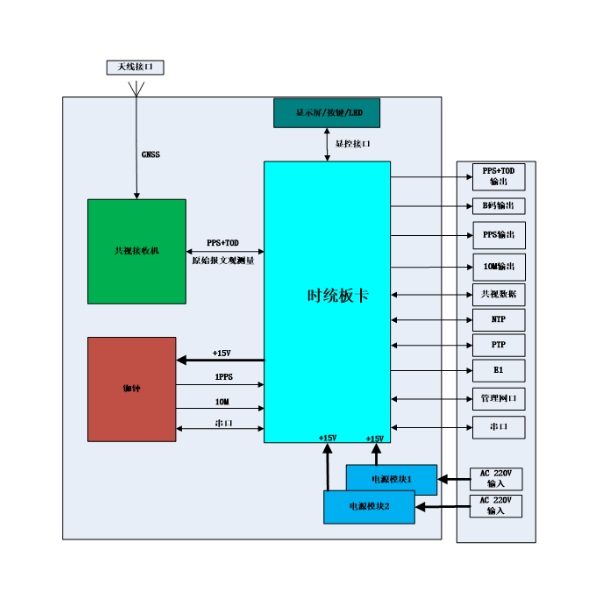

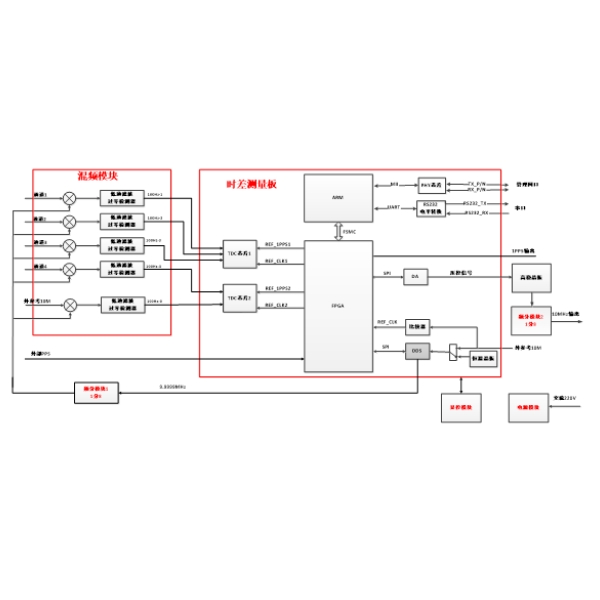

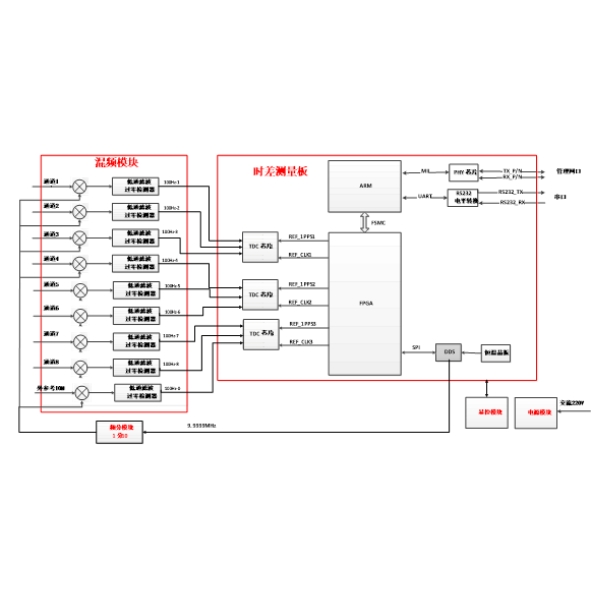

晶振&原子钟  授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

智能电网

智能电网

通信网络

通信网络

智慧交通

智慧交通

智能楼宇

智能楼宇

数据中心

数据中心

前沿领域

前沿领域

新闻资讯

新闻资讯

联系我们

联系我们

人才研学中心

人才研学中心

加入赛思

加入赛思

关于赛思

关于赛思